数字电路(第一部分:基础知识+组合电路)

进制转换

- R进制数 -> 十进制数:加权求和

- 十进制数 -> R进制数:整数除以R取余数(商为0为止,倒序排列),小数乘以R取整数(直到小数为0或达到精度要求,正序排列)

- 二进制数 -> 八进制数:以小数点为界,分别往高、往低每3位为一组,最后不足3位时用0补充然后写出每组对应的八进制字符,即为对应八进制数。

- 八进制数 -> 二进制数:1位变3位

- 二进制数 -> 十六进制数:以小数点为界,分别往高、往低每4位为一组,最后不足4位时用0补充然后写出每组对应的十六进制字符,即为对应十六进制数。

- 十六进制数 -> 二进制数:1位变4位

编码

BCD编码

格雷(Gray)码

任意两个相邻码之间只有一个位不同,这一特点可以减少码在形成、变换和传输时引起的错误。

Gn=Bn, Gi=Bi+1⊕Bi, (其中 i != n 感谢@CN.TTDragon )

数的表示

- 正数的原码、反码、补码的表示方法相同

- 负数的原码(数值位取反,符号位不变)->反码; 反码+1->补码

补码与原码相互转换,其运算过程是相同的,不需要额外的硬件电路。

- 原码取反+1->补码

- 补码取反+1->原码

溢出:运算结果超出机器数所能表示的范围

溢出判断:“变形补码”(双符号位是模4补码),采用多符号位的补码。运算结果的双符号位可能是:

- 00:结果为正,无溢出

- 01:正溢(大于机器所能表示的最大正数)

- 10:负溢(小于机器所能表示的最小负数)

- 11:结果为负,无溢出

逻辑函数及化建化简

n个变量的逻辑函数中,包含全部变量的乘积项称为最小项。n变量逻辑函数的全部最小项共有2n个。(与之相对的是最大项)

卡诺图化简

卡诺图:用小方格来表示最小项,一个小方格代表一个最小项,然后将这些最小项按照相邻性排列起来(00 01 11 10)。

2^n个相邻的最小项结合,可以消去n个取值不同的变量而合并为1项。

卡诺图合并的原则(画圈的原则)

(1)尽量画大圈,但每个圈内只能2^n(n=0,1,2,3……)个相邻项。要特别注意对边相邻性和四角相邻性。

(2)圈的个数尽量少。

(3)卡诺图中所有取值为1的方格均要被圈过,即不能漏下取值为1的最小项。

(4)在新画的包围圈中至少要含有1个末被圈过的1方格,否则该包围圈是多余的。

(5)圈组时应从合并奇异“1”单元开始,先找奇异“1”单元,圈质主蕴涵项,再圈其它项。

(6)能扩大卡诺圈时,把无关项包含进来,否则舍弃无关项。

组合逻辑电路

逻辑门电路

与门,或门,非门,与非门,或非门,异或门

混合逻辑中逻辑符号的变换:

- 逻辑图中任一条线的两端同时加上或消去小圆圈,其逻辑关系不变。

- 任一条线一端上的小圆圈移到另一端,其逻辑关系不变。

- 一端消去或加上小圆圈,同时将相应变量取反,其逻辑关系不变。

电路分析

组合逻辑电路:电路任一时刻的输出状态只决定于该时刻各输入状态的组合,而与电路的原状态无关。

步骤

- 由逻辑图写出输出端的逻辑表达式;

- 化简逻辑表达式;

- 列出真值表;

- 根据真值表或逻辑表达式,确定其功能。

电路设计

1 列逻辑真值表

- 选取输入变量和输出变量

- 逻辑赋值:用0和1分别代表不同状态

- 根据实际逻辑问题的因果关系列出逻辑真值表

2 写出逻辑函数表达式:由真值表写出逻辑函数表达式

3 对逻辑函数式进行化简和变换:根据逻辑门类型,将函数式化简或变换为最简式(与非/或非/其他)

4 画出逻辑电路图:根据/选择器件型号,由逻辑函数式,画出门级逻辑电路图

组合逻辑模块

编码器

编码器:将特定的逻辑信号编为一组二进制代码的逻辑部件。(如:输入I0…I7 输出A0…A3)

二进制编码器:任何时刻只允许输入一个有效信号,不允许同时出现两个或两个以上的有效信号,因而其输入是一组有约束(互相排斥)的变量。

优先编码器:允许同时输入两个以上信号,并按优先级输出。例如:10-4线(如74LS147)、 8-3线(如74LS148)。

译码器

译码器:将输入代码转换成特定的输出信号。(将二进制码翻译成一定的数字、字符或信息)

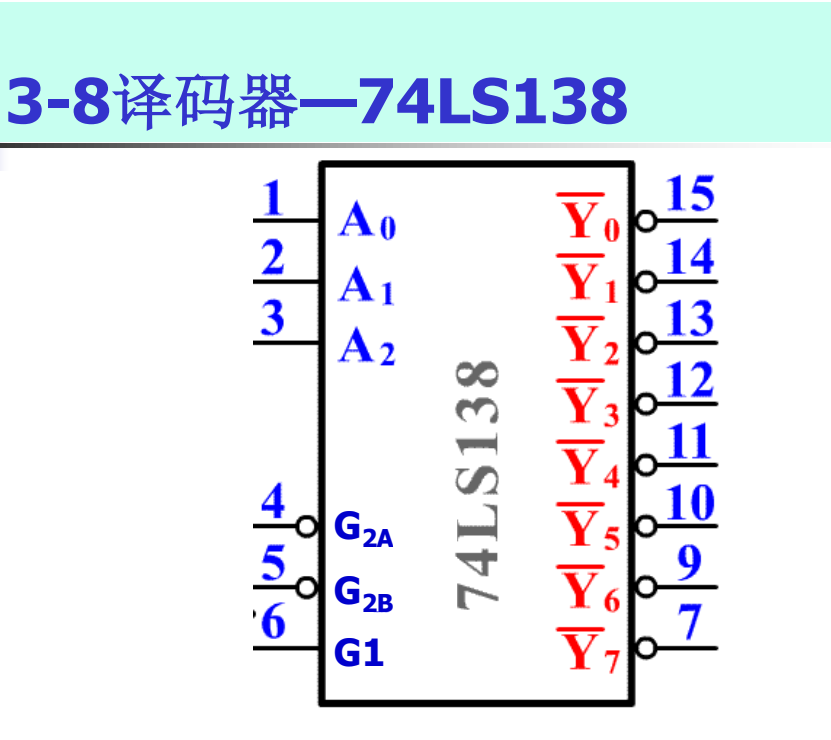

3-8译码器—74LS138

- 当G1=0时,无论其他输入信号是什么,输出都是高电平,即无效信号。

- G2A或G2B 为高电平时,输出也都是无效信号。

- 在G1=1, G2A + G2B =0时,输出信号才取决于输入信号A2、A1、A0的组合。(感谢@CN.TTDragon)

74LS138应用1 实现逻辑函数:将逻辑函数转换成最小项表达式,再转换成与非—与非形式。用一片74138加与非门就可实现三变量逻辑函数。

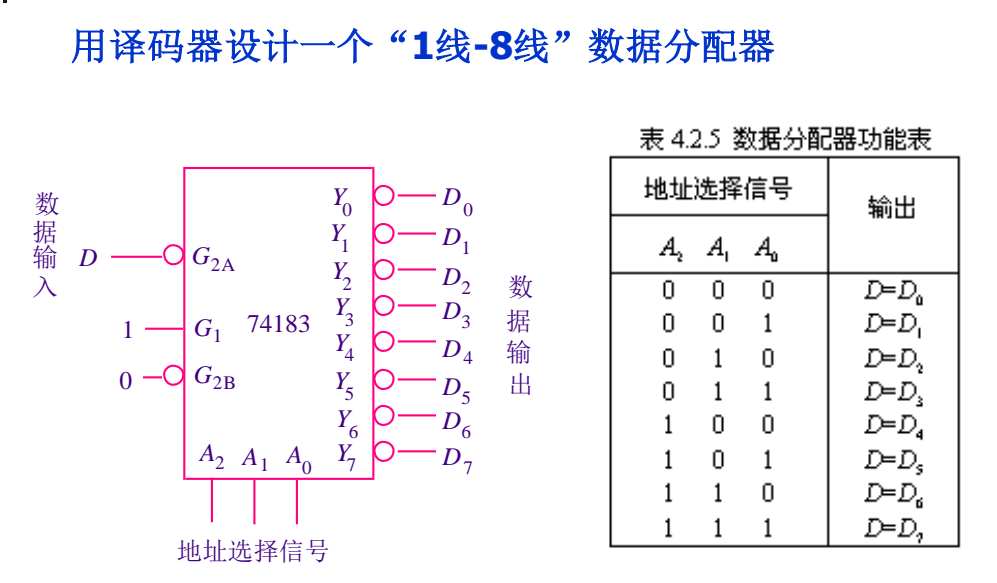

74LS138应用2 构成数据分配器:将一路输入数据根据地址选择码分配给多路数据输出中的某一路输出。

数据选择器

数据选择器:根据地址选择码从多路输入数据中选择一路,送到输出。

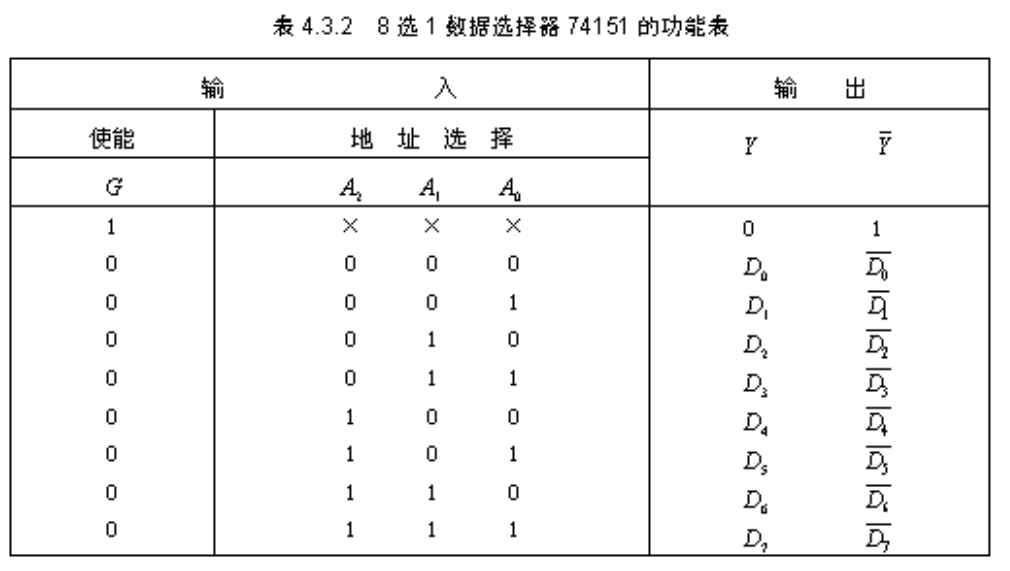

8选1数据选择器74151

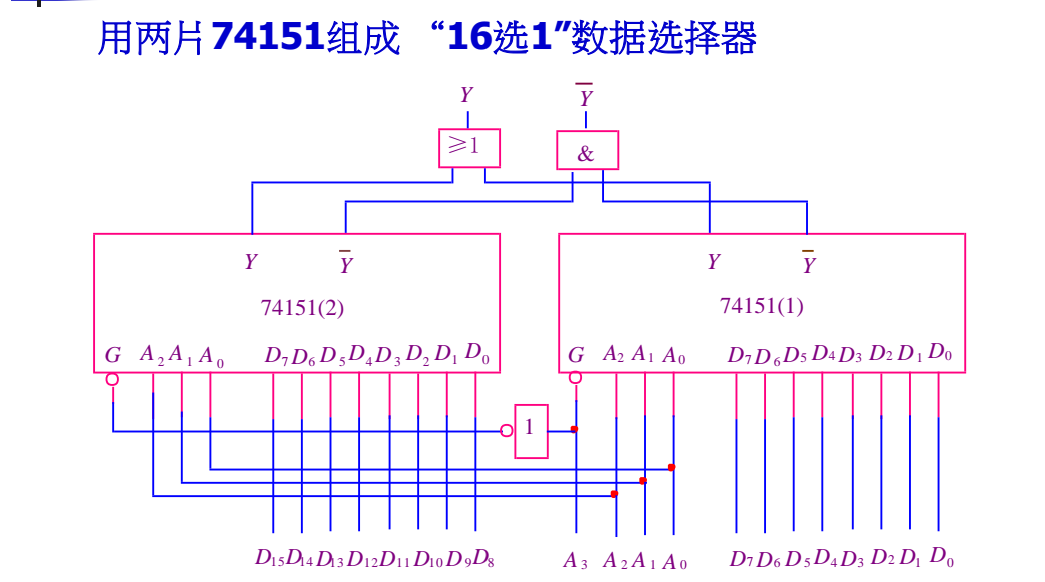

用两片74151组成 “16选1”数据选择器

数据选择器实现组合逻辑函数

-

三变量 74151:将逻辑函数转换成最小项表达式,输入变量接地址端,数据输入端按最小项接1

-

三变量 4选1 或 四变量 74151:输入变量接地址端,多出来的用卡诺图合并,选择接到合适的数据输入端

-

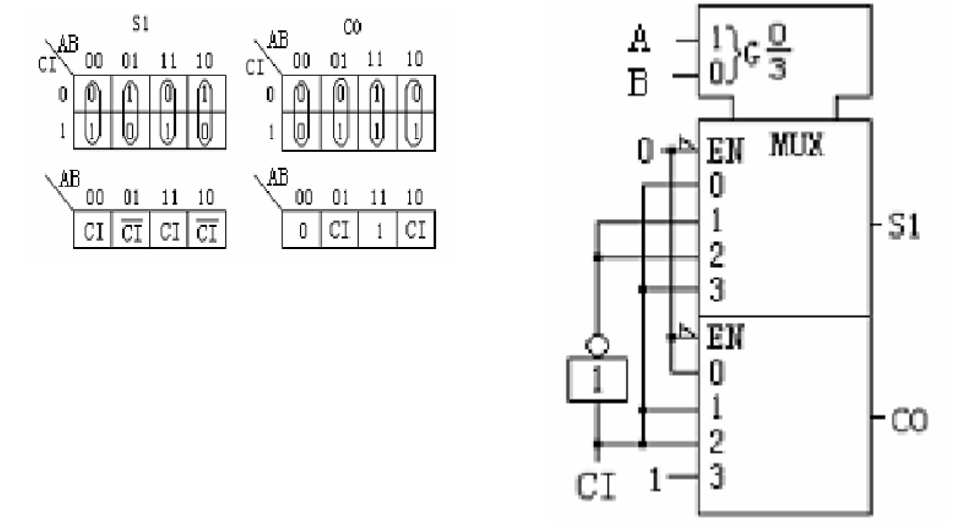

三变量 双4选1 74153:(实现1位全加器)CI为数据收入端接入的变量,A,B作为数据选择器的地址端,由卡诺图得到数据输入

About this Post

This post is written by Holger, licensed under CC BY-NC 4.0.